Con el continuo progreso de la tecnología de semiconductores, el carburo de silicio (SiC), como material de alto rendimiento, ha mostrado un gran potencial de aplicación en el campo de los dispositivos electrónicos de potencia. Sin embargo, en el proceso de preparación del sustrato de carburo de silicio, el control de calidad de la superficie es particularmente crítico, especialmente después de adelgazar, esmerilar y pulir y otros procesos para obtener una superficie ultralisa. Entre ellos, el pulido químico mecánico (CMP), como uno de los pasos clave, es de gran importancia para eliminar la capa dañada dejada por el proceso anterior y conseguir una alta nivelación superficial. Sin embargo, el proceso CMP tradicional enfrenta el problema de la baja tasa de eliminación de material (MRR), que afecta directamente la eficiencia y el costo de la producción. Por lo tanto, la exploración de nuevas tecnologías para mejorar la eficiencia CMP del sustrato de SiC se ha convertido en el foco de la investigación actual.

1. Principios básicos y desafíos del sustrato de SiC CMP

La profundidad del daño superficial del sustrato de SiC diluido o molido suele ser de 2 a 5 μm y requiere tratamiento adicional con CMP.

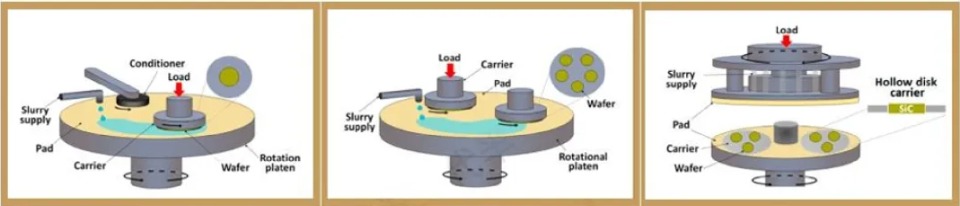

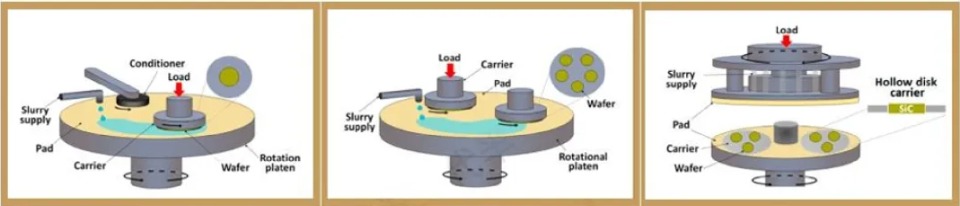

La tecnología CMP se basa en el principio compuesto "químico + mecánico", mediante la combinación de formación de capa de óxido y eliminación mecánica, para lograr el alisado de la superficie.

2. El bajo MRR es el principal problema del CMP del sustrato de SiC, y la eficiencia del CMP del SiC es significativamente menor que la del sustrato de silicio.

El impacto de un MRR bajo en la eficiencia y el costo de la producción:

Un MRR más bajo da como resultado pasos CMP de sustrato de SiC que consumen más tiempo, lo que aumenta el tiempo y el costo de procesamiento.

Incluso si el método CMP existente puede producir un sustrato 4H-SiC calificado, la baja eficiencia sigue siendo el cuello de botella que restringe su aplicación a gran escala.

Proceso de pulido CMP

3. Progreso técnico para mejorar la eficiencia de CMP:

Para afrontar el desafío del bajo MRR, la industria ha desarrollado una tecnología de pulido por lotes de doble cara.

Estas tecnologías avanzadas han reducido significativamente las horas de trabajo de CMP, como el tiempo de pulido de CMP para un solo lote de 10 sustratos de 3-5 horas a 1 hora.

La tecnología de pulido de doble cara no solo mejora la eficiencia, sino que también ayuda a mantener la consistencia y la planitud en ambos lados del sustrato.

En resumen, la mejora de la eficiencia del pulido químico-mecánico del sustrato de carburo de silicio es la clave para promover su amplia aplicación. Mediante el desarrollo de tecnologías avanzadas como el pulido de doble cara y por lotes, el problema de la baja tasa de eliminación de material en el proceso CMP tradicional se resuelve de manera efectiva, el tiempo de procesamiento se acorta significativamente y el costo de producción se reduce. En el futuro, con la mejora continua de los requisitos de rendimiento de los materiales de SiC y la innovación continua de la tecnología de pulido, tenemos razones para creer que la preparación de sustratos de SiC será más eficiente y económica, sentando una base sólida para el desarrollo futuro de Dispositivos electrónicos de potencia. Por lo tanto, la exploración y optimización continua del proceso CMP será una forma importante de promover la amplia aplicación de materiales de SiC en el campo de los semiconductores.